FPGA Pong (EC311)

Overview

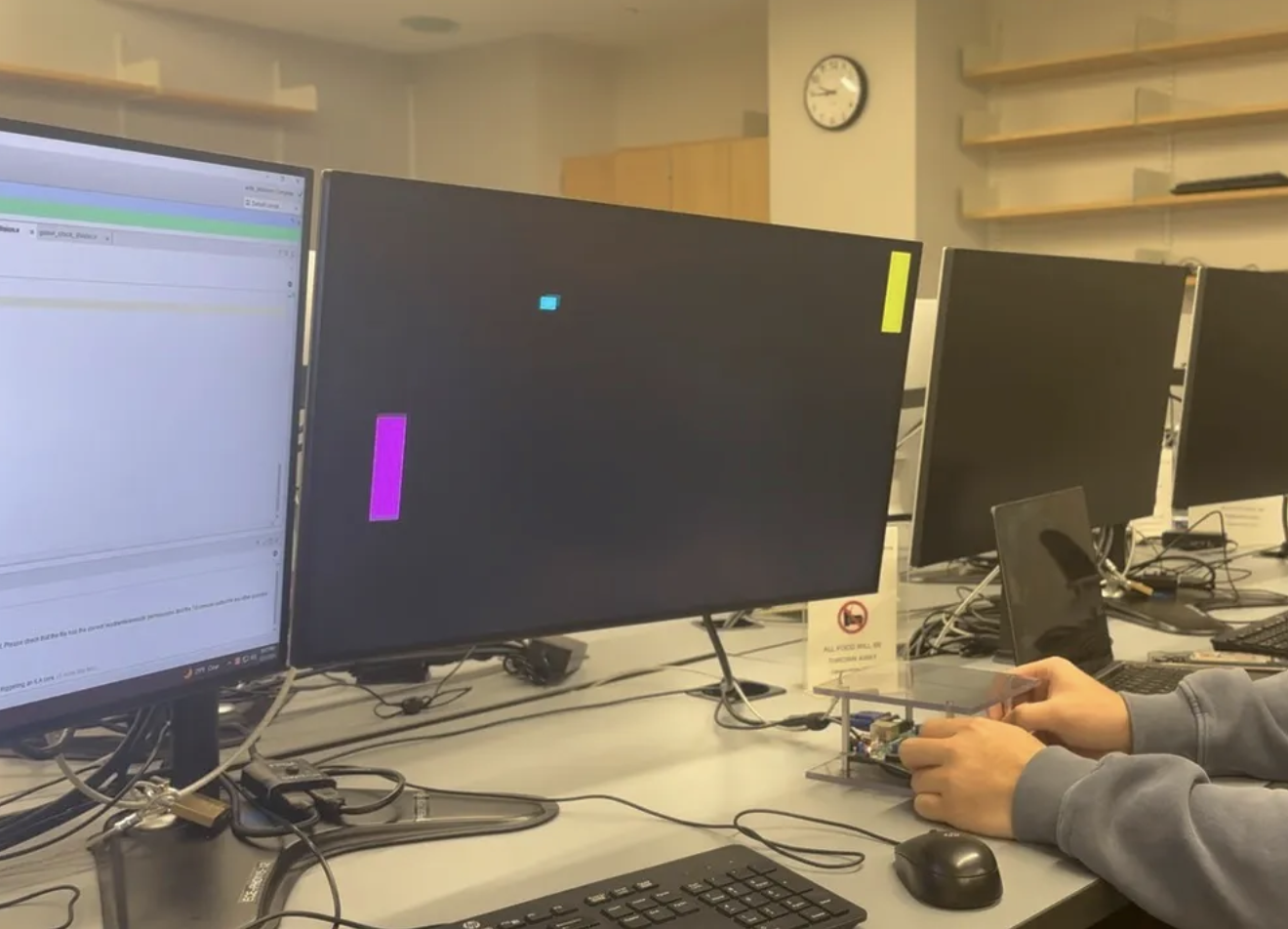

A hardware implementation of the classic Pong game built entirely in Verilog and deployed on FPGA. The system outputs real-time VGA graphics, reads paddle input from onboard switches, and updates game state in hardware using simple collision logic and finite-state machines.

Technologies Used

- HDL: Verilog

- Tools: Vivado

- Hardware: Nexys™4 DDR Artix-7 FPGA, VGA Display

Key Features

- Real-time VGA output (640×480 @ 60Hz)

- Hardware ball physics + collision detection

- Paddle control via switches/buttons

- Live score display on 7-segment LEDs

Contributions

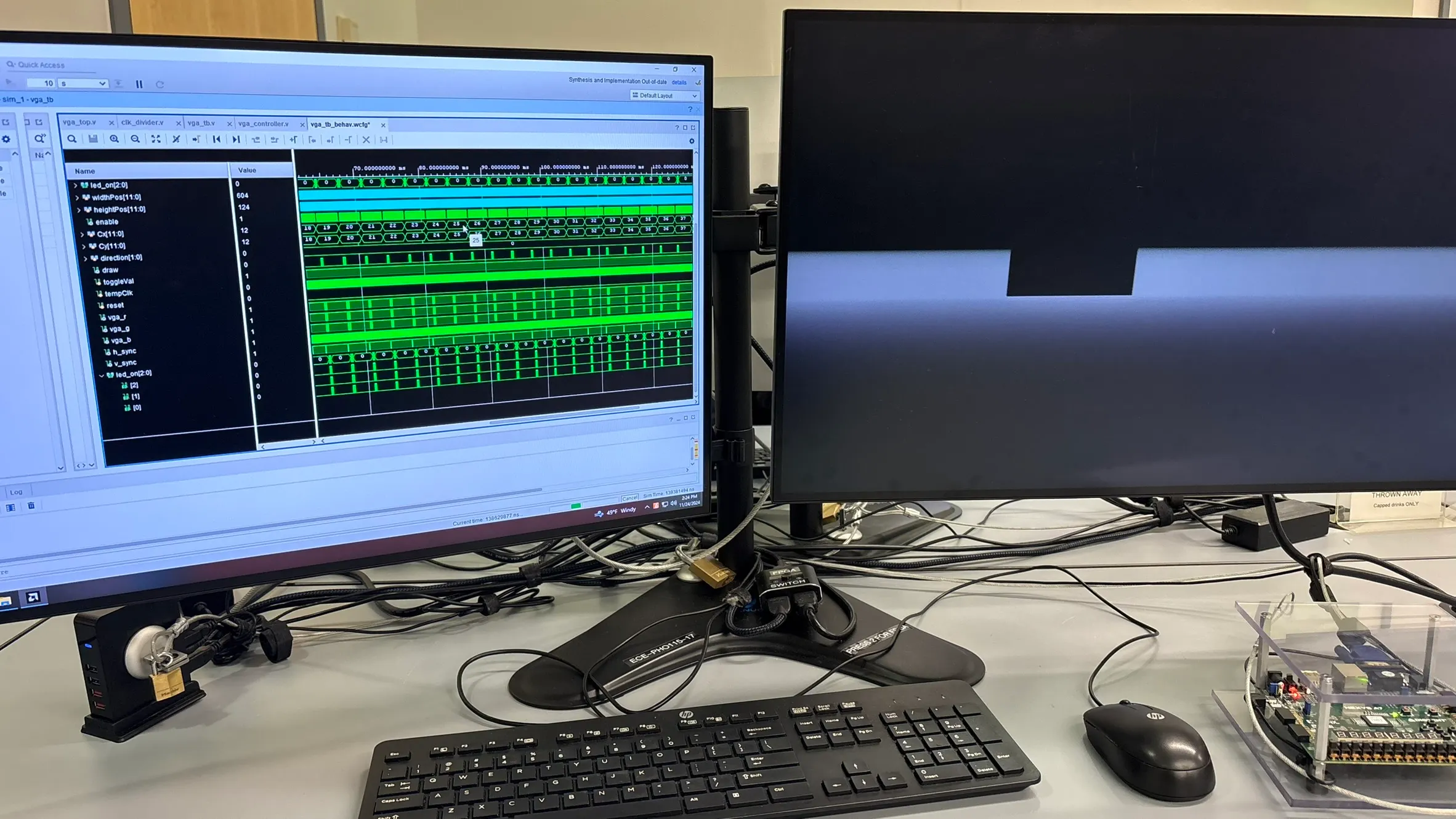

I worked on implementing and integrating core modules including ball movement, paddle control, and basic collision logic. I also contributed to the top-level VGA pipeline, wiring modules together, validating timing in simulation, and debugging rendering glitches during hardware bring-up.

Challenges

This was my first time building an interactive system fully in hardware, so managing VGA timing, clock division, and synchronous logic took careful debugging. Early versions had misaligned coordinates, unstable sync signals, and inconsistent collision checks. Through simulation and hardware testing, I learned how to structure HDL cleanly and fix timing-related issues.

Developed for my EC311 Logic Design final project @ Boston University, December 2024

Other Photos

Simulation waveform during debugging VGA output